今天,5G 蜂窝初创公司 EdgeQ 宣布其顾问委员会增加了两名新成员——前高通首席执行官保罗·雅各布斯和前高通首席技术官马特·格罗布。他们的使命是通过利用和扩展开放式硬件 RISC-V 设计,将 5G 蜂窝基站的总拥有成本 (TCO) 减半。

传统上,无线电接入网络 (RAN) 设备往往是封闭式设计和高度专有的——很像消费级 Wi-Fi 和网络硬件,它们依赖于带有供应商提供的驱动程序和固件的封闭式设计 ASIC。这种封闭的堆栈通常无法升级以适应新的协议和用例——例如,为 4G 网络设计的无线电单元或分布式单元通常必须整体更换,以便为 5G 设备提供服务。

相比之下,供应商可以实施自己的OpenRAN解决方案,这些解决方案通常在硬件中实现较少的功能,而在运行在 Linux 等传统操作系统上的软件中实现的功能较多。但正确实施这样的 O-RAN 需要非常深入的协议专业知识才能正确实施,而且一旦完成,往往非常耗电且维护成本高昂。

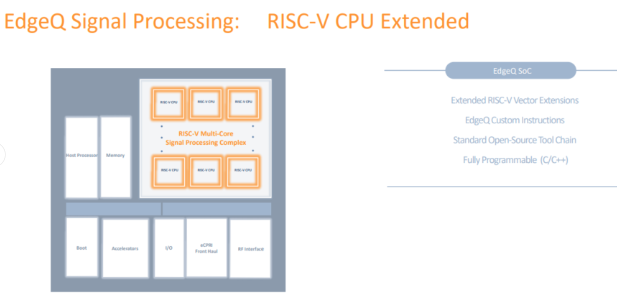

EdgeQ 的方法是有效地划分传统的封闭硅方法和昂贵的 O-RAN 之间的差异。EdgeQ 获得了参考 RISC-V CPU 设计的许可,并添加了新的硬件指令,以加速处理 4G 和 5G 通信和信号处理所需的计算成本高昂的矢量数学运算。

EdgeQ 的副总裁兼产品管理负责人 Adil Kidwai 表示,新指令不是标准的RVV矢量数学扩展。Kidwai 将 EdgeQ 的 ISA 扩展描述为一组“定制矢量指令,可在低功耗下为 5G 基础设施解决方案实现高性能”。

据 EdgeQ 首席执行官 Vinay Ravuri 称,该公司的创新方法将功耗从 100W(使用基于 Xeon 的解决方案)降低到 10W,几乎所有工作都在 EdgeQ 的 SoC 本身中完成。在蜂窝塔的 DU 中,这可能意味着将用于机器学习加速、定时器同步、FEC 加速、前端和中程传输以及 L1 处理的单独硬件全部压缩到单个 EdgeQ SoC 中,并且再次根据 EdgeQ 的说法,将 TCO 降低高达 50%。

由于 5G 信号处理和通信所需的矢量数学指令与机器学习任务所需的基本相同,因此 EdgeQ 的 CPU 中多余的处理能力可以分配给本地 ML 处理。根据 Ravuri 的说法,蜂窝通信是一种突发性工作负载,CPU 大部分时间都处于空闲状态。RISC-V CPU 的内核可以直接分区,一些分配给 4G/5G,一些分配给 ML,或者可以在服务质量 (QoS) 管理的基础上分配工作负载。

我们认为 EdgeQ 设计最重要的部分是它的灵活性。通过为客户提供对其 RISC-V SoC 的真正 C/C++ 访问,EdgeQ 不仅实现了创新,而且实现了未来的适应性。这样的系统可以就地更新以适应未来的协议升级,在这种情况下,不太灵活的系统需要“叉车升级”——这意味着你抬起旧的,滑入新的,然后把旧的推到回收站.

EdgeQ 远不是这个通用领域中唯一的公司——硬盘供应商西部数据和希捷已经开始在一些即将推出的硬件设计中实施 RISC-V 设计,并且出于类似的原因他们一直在这样做。我们希望看到 RISC-V 设计向以前封闭的硅空间的这种扩展继续下去——尤其是在消费 Wi-Fi 世界中,随着协议的变化,其更大的可编程性可能会减轻电子垃圾的增加。